题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

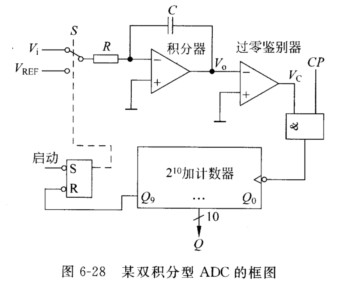

图6-28是某双积分型ADC的框图,若时钟频率为1MHz,分辨率为十位,试问: (1)最高取样频率.fS为

图6-28是某双积分型ADC的框图,若时钟频率为1MHz,分辨率为十位,试问: (1)最高取样频率.fS为多少? (2)当输入模拟电压Vi=5V时,参考电压VREF=-10V时,输出二进制代码是多少? (3)Vi=3.75V时,第一次积分时间T1和第二次积分时间△t分别是多少? (4)转换结束后,计数的状态如何?

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“图6-28是某双积分型ADC的框图,若时钟频率为1MHz,分…”相关的问题

更多“图6-28是某双积分型ADC的框图,若时钟频率为1MHz,分…”相关的问题

.jpg)

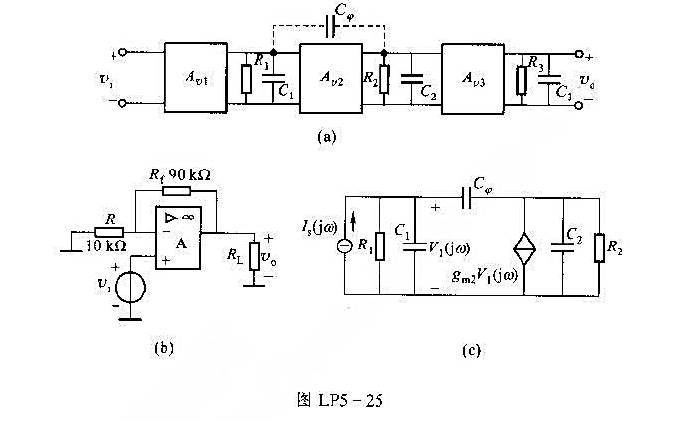

试求两种补偿时所需的电容值.设密勒补偿时

试求两种补偿时所需的电容值.设密勒补偿时 各级的输入和输出电阻对电路影响忽略不计.

各级的输入和输出电阻对电路影响忽略不计.