题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

根据取指操作所需的微操作命令,采用直接编码方式,定义控制字段每一位代表的微命令名称,并列出完

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“根据取指操作所需的微操作命令,采用直接编码方式,定义控制字段…”相关的问题

更多“根据取指操作所需的微操作命令,采用直接编码方式,定义控制字段…”相关的问题

设CPU内的部件有:PC、IR、MAR、MDR、ACC、ALU、CU,且采用非总线结构。 (1)写出取指周期的全部微操作。 (2)写出取数指令LDA X,存数指令STA X,加法指令ADD X(X均为主存地址)在执行阶段所需的全部微操作。 (3)当上述指令均为间接寻址时,写出执行这些指令所需的全部微操作。 (4)写出无条件转移指令JMP Y和结果为零则转指令BAZ Y在执行阶段所需的全部微操作。

设CPU内部采用总线连接方式,如图9.6所示。 (1)写出完成LDA X,STA X,ADD X(X均为主存地址)三条指令所需的全部微操作,并指出哪些控制信号有效。 (2)当上述三条指令均为间接寻址时,写出完成这些指令所需的全部微操作命令,并指出哪些控制信号有效。

假设X、Y、Z寄存器均为16位(最高位为第0位)。在乘法开始前,被乘数已存于X中,并用Y//Z存放乘积。 (1)画出实现补码Booth算法的运算器框图。 (2)假设CU为组合逻辑控制,且采用中央控制和局部控制相结合的办法,写出完成MUL α指令(α为主存地址)的全部微操作命令及节拍安排(包括取指阶段)。 (3)指出哪些节拍属于中央控制节拍,哪些节拍属于局部控制节拍,局部控制最多需几拍?

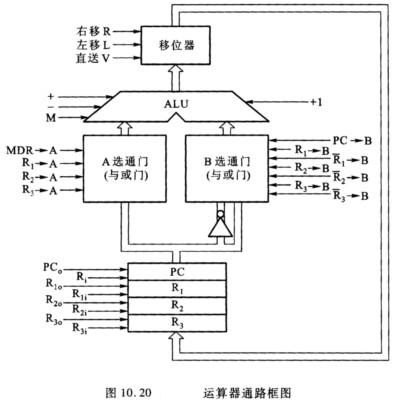

设有一运算器通路如图10.20所示,假设操作数a和b(均为补码)已分别放在通用寄存器R1和R2中,ALU有+、-、M(传送)三种操作功能。

(1)指出互斥性微操作和相容性微操作。 (2)采用字段直接编码控制方式,设计适合此运算器的微指令格式。 (3)画出计算(a-b)/2→R2的微程序流程图,试问执行周期需要几条微指令? (4)按设计的微指令格式,写出(3)要求的微指令码点。

(1)指出互斥性微操作和相容性微操作。 (2)采用字段直接编码控制方式,设计适合此运算器的微指令格式。 (3)画出计算(a-b)/2→R2的微程序流程图,试问执行周期需要几条微指令? (4)按设计的微指令格式,写出(3)要求的微指令码点。

某模型机共有64种操作,操作码位数固定,且具有以下特点: (1)采用一地址或二地址格式; (2)有寄存器寻址、直接寻址和相对寻址(位移量为-128~+127)三种寻址方式; (3)有16个通用寄存器,算术运算和逻辑运算的操作数均在寄存器中,结果也在寄存器中; (4)取数/存数指令在通用寄存器和存储器之间传送数据; (5)存储器容量为1 MB,按字节编址。 要求设计算术逻辑指令、取数/存数指令和相对转移指令的格式,并简述理由。

A.编码表示法比直接表示法的微指令字长短

B.直接表示法比编码表示法的微指令字长短

C.编码表示法与直接表示法的微指令字长是相等的

D.编码表示法与直接表示法的微指令字长大小关系不确定

A.两种控制方式的微指令位数一样 .

B.隐式编码的微指令位数多于显式编码的微指令位数

C.直接控制方式的微指令位数最长