题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

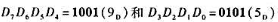

设计一个码转换电路,当输入ABCD为842l BCD码时,输出WXYZ为输入对9的补码。可以用任何门电路实现。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“设计一个码转换电路,当输入ABCD为842l BCD码时,输…”相关的问题

更多“设计一个码转换电路,当输入ABCD为842l BCD码时,输…”相关的问题

试用八选一数据选择器CT4151(逻辑符号图3.2.45)设计一个四舍五入电路。输入为8421BCD码,当输入量DCBA大于等于5时,输出Z为1,否则输出Z为0。

试用1片八D锁存器74HC373设计一个能锁存两组BCD码信号的锁存电路。假定三态输出使能端 ,锁存器原输出为

,锁存器原输出为 ,输入为

,输入为 ,画出锁存器锁存新数据前、后使能端LE应输入的波形和相应Q0的波形。

,画出锁存器锁存新数据前、后使能端LE应输入的波形和相应Q0的波形。