题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

n位异步二进制加法计数器由n个()组成,最低位触发器的时钟端与()相连;如果触发器的时钟是下降

n位异步二进制加法计数器由n个()组成,最低位触发器的时钟端与()相连;如果触发器的时钟是下降

沿有效,则高位触发器的时钟端与相邻低位触发器的()相连;如果是上升沿有效,则与()相连。

暂无答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

沿有效,则高位触发器的时钟端与相邻低位触发器的()相连;如果是上升沿有效,则与()相连。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“n位异步二进制加法计数器由n个()组成,最低位触发器的时钟端…”相关的问题

更多“n位异步二进制加法计数器由n个()组成,最低位触发器的时钟端…”相关的问题

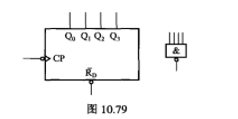

用异步清零端 和一个与非门(见图10.79),用反馈归零法将4位二进制加法计数器接成13进制计数器,请将线路图连接画出.

和一个与非门(见图10.79),用反馈归零法将4位二进制加法计数器接成13进制计数器,请将线路图连接画出.

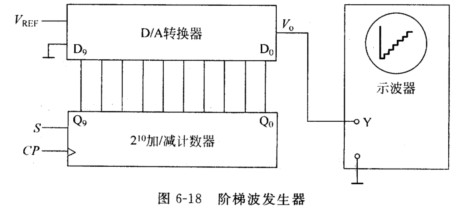

如图所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),时钟频率为1MHz,求阶梯波的重复周期,试画出加法计数和减法计数时DAC的输出波形(控制信号S=0,加计数;S=1,减计数)。

图6-18所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),时钟频率为1 MHz,求阶梯波的重复周期,试画出加法计数和减法计数时DAC的输出波形(控制信号S=0,加计数;S=1,减计数)。