题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

CPU访问存储器的时间是由存储器的容量决定的,存储器容量越大,访问存储器所需要的时间就越长。()

CPU访问存储器的时间是由存储器的容量决定的,存储器容量越大,访问存储器所需要的时间就越长。( )

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

CPU访问存储器的时间是由存储器的容量决定的,存储器容量越大,访问存储器所需要的时间就越长。( )

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“CPU访问存储器的时间是由存储器的容量决定的,存储器容量越大…”相关的问题

更多“CPU访问存储器的时间是由存储器的容量决定的,存储器容量越大…”相关的问题

由于CPU内部操作的速度较快,而CPU访问一次存储器的时间较长,因此机器周期通常由()来确定。

A.指令周期

B.存取周期

C.间址周期

D.中断周期

A.主存存放正在CPU 中运行的程序,速度较快,容量很大

B.Cache 存放当前所有频繁访问的数据,特点是速度最快、容量较小

C.外存存放需联机保存但暂时不执行的程序和数据,容量很大且速度很慢

D.外存存放需联机保存但暂时不执行的程序和数据,容量很大且速度很快

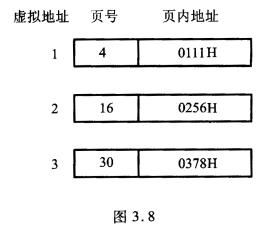

图3.8表示用快表(页表)进行虚实地址转换的条件,快表放在相联存储器中,其容量为8个存储单元,问: (1)当CPU按虚似地址l去访问主存储器时,主存储器的实际地址是多少? (2)当CPU按虚拟地址2去访问主存储器时,主存储器的实际地址是多少? (3)当CPU按虚拟地址3去访问主存储器时,主存储器的实际地址是多少?

设某机共能完成120种操作,CPU有8个通用寄存器(12位),主存容量为16K字,采用寄存器—存储器型指令。 (1)欲使指令可直接访问主存的任一地址,指令字长应取多少位? (2)若在上述设计的指令字中设置一寻址特征位X,且X=0表示某个寄存器作基址寄存器,画出指令格式。试问采用基址寻址可否访问主存的任一单元?为什么?如不能,提出一种方案,使指令可访问主存的任一位置。 (3)若指令字长等于存储字长,且主存容量扩大到64K字,在不改变硬件结构的前提下,可采用什么方法使指令可访问存储器的任一位置?