题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

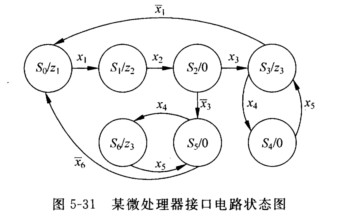

试用S0~S6的状态画出110000串行序列检测器的状态图,当输入完成上述串行输入时,输出才为1。

(2)求符合该题要求的最简状态图(表)。

(2)求符合该题要求的最简状态图(表)。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

(2)求符合该题要求的最简状态图(表)。

(2)求符合该题要求的最简状态图(表)。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“试用S0~S6的状态画出110000串行序列检测器的状态图,…”相关的问题

更多“试用S0~S6的状态画出110000串行序列检测器的状态图,…”相关的问题

试用74181和74182器件设计以下两种方案的32位ALU(只需画出进位之间的联系),并比较两种方案的速度及集成电路片数。 (1)采用单重分组(组内并行进位,组间串行进位)进位结构; (2)采用双重分组(二级先行进位)进位结构。

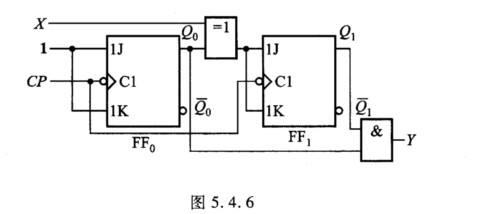

试用同步时序电路分析方法分析图5.4.6所示电路,画出状态图和波形图,确定电路的逻辑功能(设触发器的初始状态均为0)。

画出如图(a)所示电路中S1、S0、C1的波形图,其中,A1、A0、B1、B0、C0的波形如图(b)所示。

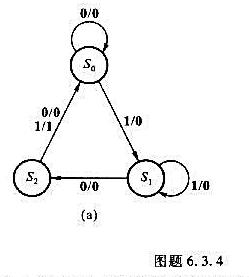

.3.4(a)。

设计一个带有选择变量S1和S0的算术运算电路,实现表给出的算术运算操作,并画出其逻辑电路图。

| 选择变量 | 输 出 | |

| S1S0 | Cin=0 | Cin=1 |

| 0 0 0 1 1 0 1 1 | F=A F=A-B-1 F=B-A-1 F=A+B | F=A+1 F=A-B F=B-A F=A+B+1 |