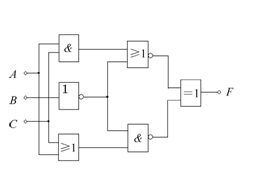

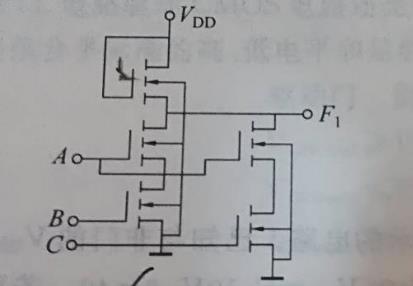

更多“试分析图(a)中输出F1的逻辑表达式。”相关的问题

更多“试分析图(a)中输出F1的逻辑表达式。”相关的问题

第2题

已知输出逻辑函数表达式为 F1(A,B,c)=∑m(2,5,6,7) F2(A,B,c)=∑m(1,2,3,4,5,6) 试

已知输出逻辑函数表达式为 F1(A,B,c)=∑m(2,5,6,7) F2(A,B,c)=∑m(1,2,3,4,5,6) 试画出:(1)由一般标准门电路构成的组合逻辑电路; (2)等效的FPLA器件的基本熔丝结构; (3)FPLA器件的映象逻辑图。

第4题

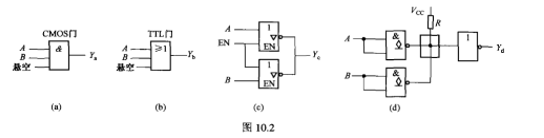

在图10.2中,欲使图(a)中的Ya=AB,图(b)中的Yb=A+B,图(c)为三态门接成总线结构的电路.试

在图10.2中,欲使图(a)中的Ya=AB,图(b)中的Yb=A+B,图(c)为三态门接成总线结构的电路.试

点击查看答案

改正下图电路的错误,使其正常工作并得到想要的输出结果:写出图(d)所示TIL门电路的输出Yd的逻辑表达式.

第5题

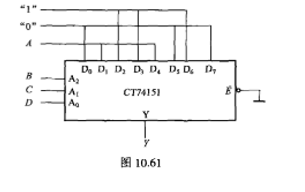

图7.6.1是一个1 6×4位的ROM,A3A2A1A。为地址输入,D3,D2,D1,D0为数据输出。若将D3,D2,D1,D0视为A3,A

2,A1,A0的逻辑函数,试写出D3,D2,D1,D0的逻辑表达式。

点击查看答案

.jpg)

第6题

由3-8译码器74LS138和逻辑门构成的组合逻辑电路如图P4-16所示。(1)试分别写出F1、F2的最简或与

由3-8译码器74LS138和逻辑门构成的组合逻辑电路如图P4-16所示。(1)试分别写出F1、F2的最简或与

点击查看答案

由3-8译码器74LS138和逻辑门构成的组合逻辑电路如图P4-16所示。

(1)试分别写出F1、F2的最简或与表达式。

(2)试说明当输入变量A、B、C、D为何种取值时,F1=F2=1。

第7题

一个l位二进制数码比较器有两个输入端A和B及两个输出端F1和F2,当A>B时,F1=1,F2=0;当A<B时,F1=0,F

2=1;当A=B时,F1=F2=1。试列出F1和F2的真值表,并分别写出F1、F2的积之和表达式和F1、F2的和之积表达式。

点击查看答案

第8题

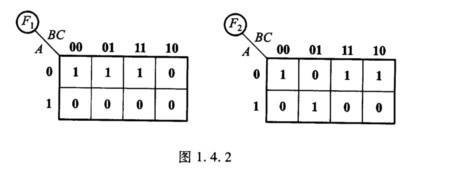

已知逻辑函数F1和F2的卡诺图如图1.4.2所示,试求F3=F1+F2的卡诺图,并化成最简或与式。

已知逻辑函数F1和F2的卡诺图如图1.4.2所示,试求F3=F1+F2的卡诺图,并化成最简或与式。

第10题

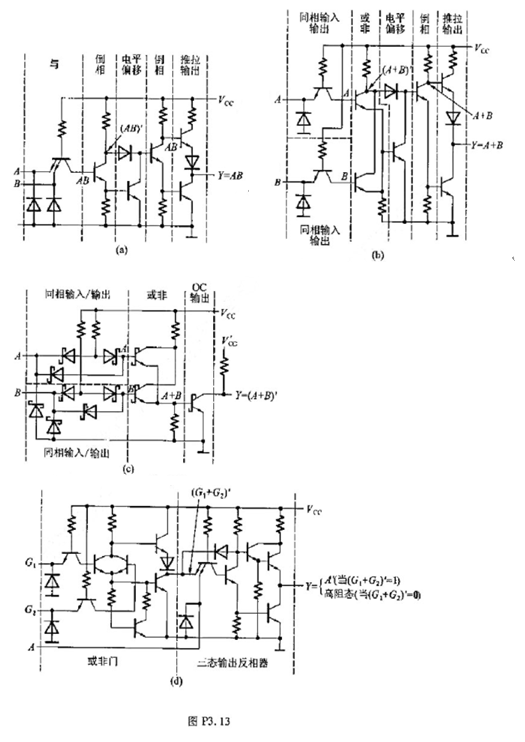

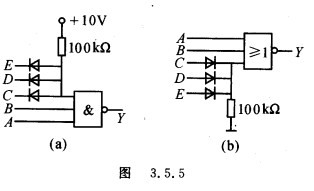

在CMOS门电路中,有时采用图3.5.5所示的方法扩展输入端。试分析图中(a),(b)所示电路的逻辑功能,写

在CMOS门电路中,有时采用图3.5.5所示的方法扩展输入端。试分析图中(a),(b)所示电路的逻辑功能,写出Y的逻辑表达式。假定VDD=10 V,二极管的正向导通压降VD=0.7 V。

如果结果不匹配,请

如果结果不匹配,请