题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

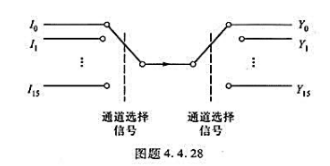

试用输出低电平有效的3线-8线译码器和逻辑门设计一组合电路。该电路输入X,输出F均为3位二进制数。二者之间关

试用输出低电平有效的3线-8线译码器和逻辑门设计一组合电路。该电路输入X,输出F均为3位二进制数。二者之间关系如下:

2≤X≤5时,F=X+2

X<2时,F=1

X>5时,F=0

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

试用输出低电平有效的3线-8线译码器和逻辑门设计一组合电路。该电路输入X,输出F均为3位二进制数。二者之间关系如下:

2≤X≤5时,F=X+2

X<2时,F=1

X>5时,F=0

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“试用输出低电平有效的3线-8线译码器和逻辑门设计一组合电路。…”相关的问题

更多“试用输出低电平有效的3线-8线译码器和逻辑门设计一组合电路。…”相关的问题

1.jpg)

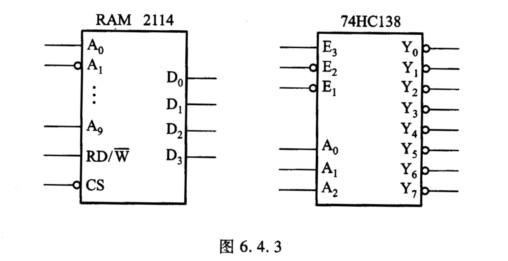

RAM 2114芯片(容量为1 K×4位)和3线-8线译码器74HCl38的简化框图如图6.4.3所示,试用这两种类型的芯片组成4 K×8位的存储器系统,写出设计思想,画出逻辑图。

由移位寄存器74HCl94和3线-8线译码器74HCl38组成的电路如图5.3.27所示,分析电路,列出状态表,并画出输出端L的波形。

1.jpg)

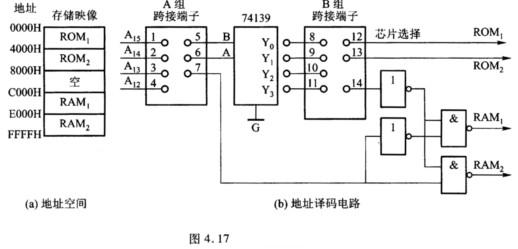

存储器的地址空间分布图和存储器的地址译码电路分别如图4.17(a)和(b)所示,图(b)中的A、B两组跨接端子可按要求分别进行接线,如1~4中的任一端子可以和5~7中的任一端子跨接。74139是2线—4线译码器(译码输出低电平有效),使能端G接地表示译码器处于正常译码状态。试完成A组跨接端子与B组跨接端子内部的连接,以便使地址译码电路按图(a)的要求进行正确寻址。