题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

下列关于TLB、cache和虚存页(Page)命中组合情况中,一次访存过程中可能发生的是()

A.TLB命中、cache命中、Page命中

B.TLB未命中、cache命中、Page命中

C.TLB未命中、cache未命中、Page命中

D.TLB未命中、cache命中、Page未命中

答案

答案

ABC

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.TLB命中、cache命中、Page命中

B.TLB未命中、cache命中、Page命中

C.TLB未命中、cache未命中、Page命中

D.TLB未命中、cache命中、Page未命中

答案

答案

ABC

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“下列关于TLB、cache和虚存页(Page)命中组合情况中…”相关的问题

更多“下列关于TLB、cache和虚存页(Page)命中组合情况中…”相关的问题

下列关于CaChe写策略的论述中,正确的是()。

A.带TLB和写回策略CaChe的CPU执行Store指令时,可能不访问主存

B.采用回写法时,无论被替换的CaChe行是否“被写过”,都要将其写回主存

C.采用全写法,CPI会增大

D.面向包含大量写操作的数据密集型应用的单处理器系统通常采用全写法

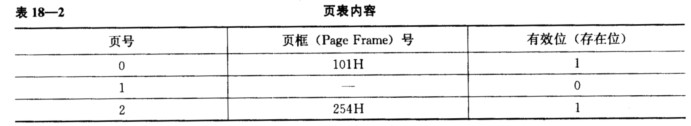

请求分页管理系统中,假设某进程的页表内容如表18—2所示。

页面大小为4KB,一次内存的访问时间是100ns,一次快表(TLB)的访问时间是10ns,处理一次缺页的平均时间为108ns(已含更新TLB和页表的时间),进程的驻留集大小固定为2,采用最近最少使用置换算法(LRU)和局部淘汰策略。假设①TLB初始为空;②地址转换时先访问TLB,若TLB未命中,再访问页表(忽略访问页表之后的TLB更新时间);③有效位为0表示页面不在内存,产生缺页中断,缺页中断处理后,返回到产生缺页中断的指令处重新执行。设有虚地址访问序列2362H、1565H、25.A5H,请问: (1)依次访问上述三个虚地址,各需多少时间?给出计算过程。 (2)基于上述访问序列,虚地址1565H的物理地址是多少?请说明理由。

页面大小为4KB,一次内存的访问时间是100ns,一次快表(TLB)的访问时间是10ns,处理一次缺页的平均时间为108ns(已含更新TLB和页表的时间),进程的驻留集大小固定为2,采用最近最少使用置换算法(LRU)和局部淘汰策略。假设①TLB初始为空;②地址转换时先访问TLB,若TLB未命中,再访问页表(忽略访问页表之后的TLB更新时间);③有效位为0表示页面不在内存,产生缺页中断,缺页中断处理后,返回到产生缺页中断的指令处重新执行。设有虚地址访问序列2362H、1565H、25.A5H,请问: (1)依次访问上述三个虚地址,各需多少时间?给出计算过程。 (2)基于上述访问序列,虚地址1565H的物理地址是多少?请说明理由。

该逻辑地址对应的页号是多少?

A.I、II、Ⅳ

B.I、Ⅳ

C.只有I

D.全都正确

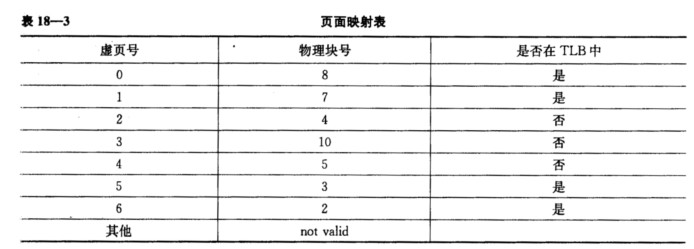

某请求页式存储管理,允许用户空间为32个页面(每页1KB),主存为16KB,如有一个用户程序有10页长,且某时刻该用户进程的页表如表18—3所示。

(1)如果程序执行时遇到以下两个虚地址:OAC5H、1AC5H,试计算它们对应的物理地址。 (2)页表存放在主存中,对主存的一次存取需要1.5微秒,对TLB表的查找时间忽略为0,试问这两次访问共耗费多少时间?

(1)如果程序执行时遇到以下两个虚地址:OAC5H、1AC5H,试计算它们对应的物理地址。 (2)页表存放在主存中,对主存的一次存取需要1.5微秒,对TLB表的查找时间忽略为0,试问这两次访问共耗费多少时间?

下列关于命中组合的情况中,一次访存过程中可能发生的是()。

A.TLB未命中,CaChe命中,Page未命中

B.TLB未命中,CaChe未命中,Page命中

C.TLB命中,CaChe命中,Page未命中

D.TLB命中,CaChe未命中,Page未命中

下列关于CaChe和虚拟存储器的说法,错误的是()。

A.当CaChe失效(即不命中)时,处理器将会切换进程,以更新CaChe中的内容

B.当虚拟存储器失效(如缺页)时,处理器将会切换进程,以更新主存中的内容

C.CaChe的速度比主存的速度大约快10倍

D.主存的速度比辅存的速度大约快100倍

如果在上一个问题中给计算机添加TLB,并且页表项有80%的时间在TLB中(即所需的存储器访问导致80%的时间在TLB中“发生”),平均来讲,读取程序存储器的一个字要花多长时间?

访问转换旁视缓冲器(快表)命中,说明()。

A.目标数据在CaChe中

B.目标数据在主存中,而且最近被访问过

C.目标数据在TLB中

D.目标数据在主存中,但最近是否被访问过不确定