题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

利用CS£1和CS£2型试块可绘制直探头()£波幅曲线和()£波幅曲线。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“利用CS£1和CS£2型试块可绘制直探头()£波幅曲线…”相关的问题

更多“利用CS£1和CS£2型试块可绘制直探头()£波幅曲线…”相关的问题

设某微机的寻址范围为64K,接有8片8K的存储芯片,存储芯片的片选信号为CS,要求: (1)画出选片译码逻辑电路(可选用74138译码器)。 (2)写出每片RAM的地址范围。 (3)如果运行时发现只有以0000H为起始地址的一片存储芯片不能读/写,分析故障原因,如何解决? (4)如果发现只能对第1~4片RAM进行读/写,试分析故障原因。

某系统结构图如图5-72所示。

试根据频率特性的物理意义,求下列输入信号作用时,系统的稳态输出Cs(t)和稳态误差es(t): (1)r(t)=sin2t。 (2)r(t)=sin(t+30°)-2cos(2t-45°)。

试根据频率特性的物理意义,求下列输入信号作用时,系统的稳态输出Cs(t)和稳态误差es(t): (1)r(t)=sin2t。 (2)r(t)=sin(t+30°)-2cos(2t-45°)。

假设(CS)=3000H,(DS)=4000H,(ES)=2000H,(SS)=5000H,(Ax)=2060H, (BX)=3000H,(CX)=5,(DX)=0,(SI)=2060H,(DI)=3000H,(43000H)=0A006H,(23000H)=0B116H,(33000H)=0F802H,(25060)=00BOH,(SP)=0FFFEH,(CF)=1, (DF)=l,试写出下列各条指令单独执行完后,有关寄存器及存储单元的内容,若影响条件标志,需给出条件标志SF、ZF、OF、CF的值。 (1)SBB AX,BX (2)CMP AX,WORD PTR[SI+0FAOH] (3)MUL BYTE PTR[BX] (d)AAM (5)DIV BH (6)SAR AX,CL (7)XOR AX.0FFE7 H (8)REP STOSB (9)JMP WORD PYR[BX] (10)XCHG AX,ES:[BX+SI]

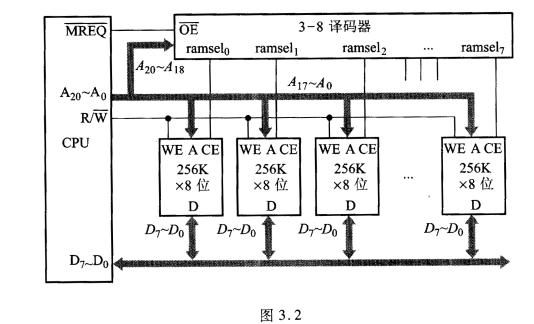

某计算机的主存地址空间中,从地址0000H~3FFFH为ROM存储区域,从地址

4000H~7FFFH为RAM的存储区域。RAM的控制信号为CS和WE,CPU的地址线为A15~A0,数据线为8位的D7~D0线,控制信号有读写控制R/W和访存请求MREQ,要求: (1)画出地址译码方案。 (2)如果ROM和RAM存储器芯片都采用8 K×1位的芯片,试画出存储器与CPU的连接图。 (3)如果ROM存储器芯片采用8K×8位的芯片,RAM存储器芯片采用4K×8位的芯片, 试画出存储器与CPU的连接图。 (4)如果ROM存储器芯片采用16K×8位的芯片,RAM存储器芯片采用8K×8位的芯片,试画出存储器与CPU的连接图。

4000H~7FFFH为RAM的存储区域。RAM的控制信号为CS和WE,CPU的地址线为A15~A0,数据线为8位的D7~D0线,控制信号有读写控制R/W和访存请求MREQ,要求: (1)画出地址译码方案。 (2)如果ROM和RAM存储器芯片都采用8 K×1位的芯片,试画出存储器与CPU的连接图。 (3)如果ROM存储器芯片采用8K×8位的芯片,RAM存储器芯片采用4K×8位的芯片, 试画出存储器与CPU的连接图。 (4)如果ROM存储器芯片采用16K×8位的芯片,RAM存储器芯片采用8K×8位的芯片,试画出存储器与CPU的连接图。

A.c升力系数,通常是通过风洞实验测的的

B.ρ飞行高度处空气密度

C.v飞机的空速,飞机相对地面的速度

D.s是机翼的平面投影面积