题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

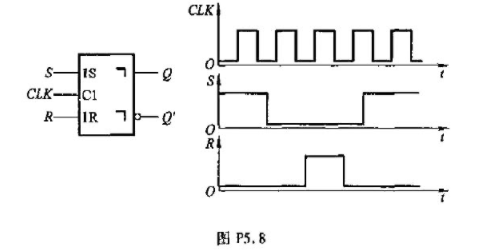

在脉冲触发SR触发器电路中,若S、R、CLK端的电压波形如图P5.8所示,试画出Q、Q'端对应的电压波

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“在脉冲触发SR触发器电路中,若S、R、CLK端的电压波形如图…”相关的问题

更多“在脉冲触发SR触发器电路中,若S、R、CLK端的电压波形如图…”相关的问题

在下列锁存器和触发器中,没有约束条件的是()。

A.基本SR锁存器

B.主从SR触发器

C.逻辑门控SR触发器

D.边沿D触发器

对于用两个或非门构成的基本SR锁存器,如果S=R=0,则触发器的状态应为()。

A.置0

B.置1

C.不变

D.不定

.jpg)

单稳态触发器正常工作时输出脉冲的宽度取决于()。

A.触发脉冲的宽度

B.触发脉冲的幅度

C.电源电压的数值

D.电路本身的电阻、电容值

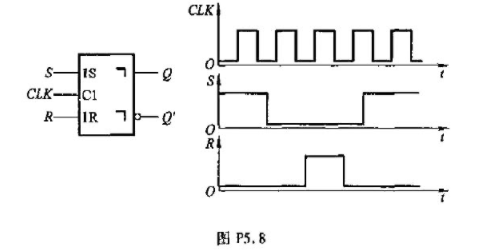

由单稳态触发器741 21构成的噪声消除电路及输入波形如图7.4.3所示。

(1)试说明消除噪声的原理,画出

(1)试说明消除噪声的原理,画出

及vO的波形; (2)若输入信号高电平持续时间为100μs,噪声宽度5μs,确定R的取值范围。

及vO的波形; (2)若输入信号高电平持续时间为100μs,噪声宽度5μs,确定R的取值范围。

若增加集成单稳态触发器输出脉冲的宽度,则()。

A.增加触发脉冲的时间间隔

B.增加电源电压的数值

C.增加外接电阻或电容值

D.减小外接电阻或电容值

由集成单稳态触发器74121所组成的电路及参数如图7.3.2(a)所示,触发输入信号如图7.3.2(b)所示。

.jpg) (1)计算在v1作用下vO1、vO2输出脉冲的宽度; (2)画出对应v1的输出vO1、vO2的波形。

(1)计算在v1作用下vO1、vO2输出脉冲的宽度; (2)画出对应v1的输出vO1、vO2的波形。

CMOS施密特与非门组成的电路如图7.3.3(a)所示,窄脉冲触发输入信号vI如图7.3.3(b)所示。已知R=5 kΩ,C=0.1μ F,VDD=5 V, VOH≈5 V,VILL≈0 V,VT+=3.3 V,VT-=1.8 V。 (1)分析电路的工作原理,画出vV及vO的波形(两个触发脉冲间隔的时间足够长)。 (2)计算输出高电平持续的时间。

1.jpg)

在图4.4.4所示电路中,设两触发器的初态均为0,经过3个

1.jpg) 脉冲作用后,Q1Q2的状态为_________________。

脉冲作用后,Q1Q2的状态为_________________。

2.jpg)