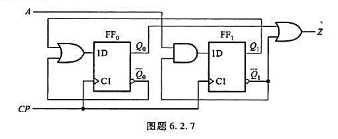

更多“试分析图题6.2.7所示同步时序电路,写出激励方程组、转换方…”相关的问题

更多“试分析图题6.2.7所示同步时序电路,写出激励方程组、转换方…”相关的问题

第1题

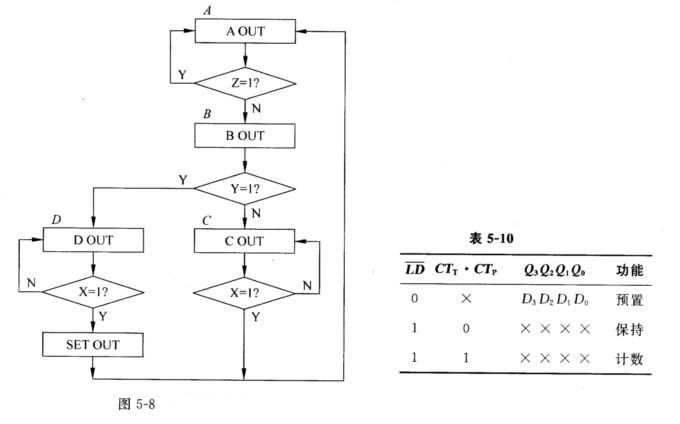

用MSI时序模块实现同步时序电路。 某系统ASM图如图5-8所示,试设计该图描述的控制器(条件输出

用MSI时序模块实现同步时序电路。 某系统ASM图如图5-8所示,试设计该图描述的控制器(条件输出块和状态块中所标符号为输出信号)。要求用集成计数器74LS163为核心进行设计。(附74LS163计数器主要功能表,如表5-10所示。)

第3题

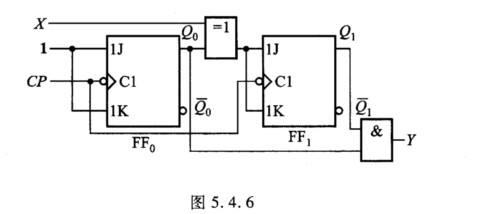

试用同步时序电路分析方法分析图5.4.6所示电路,画出状态图和波形图,确定电路的逻辑功能(设触发器

试用同步时序电路分析方法分析图5.4.6所示电路,画出状态图和波形图,确定电路的逻辑功能(设触发器的初始状态均为0)。

第4题

一个11位左移移位寄存器和两个同步时序电路相连,如图4-56(a)所示。这两个同步时序电路的状态如图4

一个11位左移移位寄存器和两个同步时序电路相连,如图4-56(a)所示。这两个同步时序电路的状态如图4-56(b)所示。设寄存器的状态为01101000100,两个时序电路均处于00状态,试确定在11个CP脉冲作用下Z2的输出序列。

.jpg)

第6题

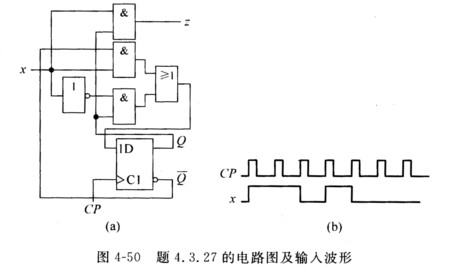

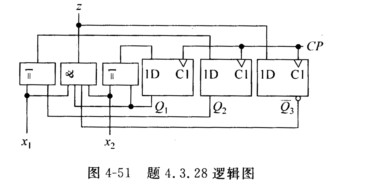

分析图4-50(a)所示同步时序电路。写出激励方程及输出方程,画出状态图,列出状态表。如初始状态为0,

分析图4-50(a)所示同步时序电路。写出激励方程及输出方程,画出状态图,列出状态表。如初始状态为0,输入信号如图4-50(b)所示,画出D、Q、z的波形图。

第8题

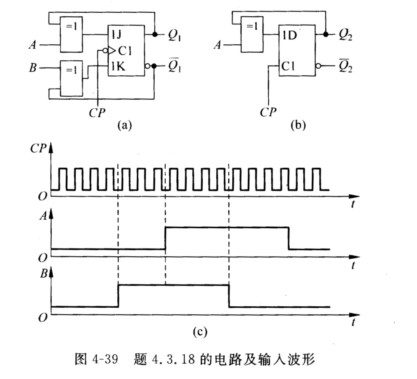

图4-39(a)、(b)所示为两个时序电路,其输入信号如图4-39(c)所示。试分别画出相应的输出波形Q1、Q2。

图4-39(a)、(b)所示为两个时序电路,其输入信号如图4-39(c)所示。试分别画出相应的输出波形Q1、Q2。

第11题

图4-59所示为由两片同步十六进制计数器组成的计数器,试说明它的模,画出在20个CP脉冲作用下各Q端

图4-59所示为由两片同步十六进制计数器组成的计数器,试说明它的模,画出在20个CP脉冲作用下各Q端的波形图。

.jpg)

如果结果不匹配,请

如果结果不匹配,请

1.jpg)

1.jpg)

1.jpg)