题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

由PLA和D触发器构成的同步时序电路如图6.3.7所示。试写出电路的驱动方程、状态方程,并列出其状态转

换真值表,并说明电路完成的逻辑功能。

1.jpg)

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

1.jpg)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“由PLA和D触发器构成的同步时序电路如图6.3.7所示。试写…”相关的问题

更多“由PLA和D触发器构成的同步时序电路如图6.3.7所示。试写…”相关的问题

A、状态数目更多

B、状态数目更少

C、触发器更多

D、触发器一定更少

用触发器实现同步时序电路。 (1)用J-K触发器设计一个模为8的格雷码同步计数器。 (2)用D触发器设计上述题目。 (3)几点说明。

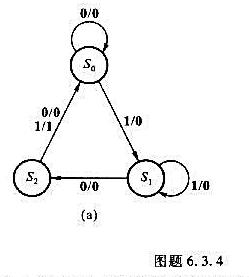

.3.4(a)。

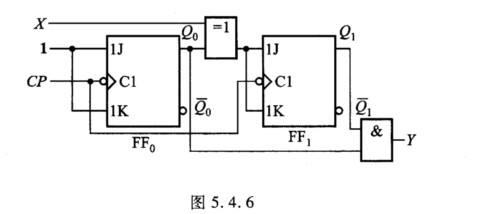

试用同步时序电路分析方法分析图5.4.6所示电路,画出状态图和波形图,确定电路的逻辑功能(设触发器的初始状态均为0)。

一个11位左移移位寄存器和两个同步时序电路相连,如图4-56(a)所示。这两个同步时序电路的状态如图4-56(b)所示。设寄存器的状态为01101000100,两个时序电路均处于00状态,试确定在11个CP脉冲作用下Z2的输出序列。

.jpg)

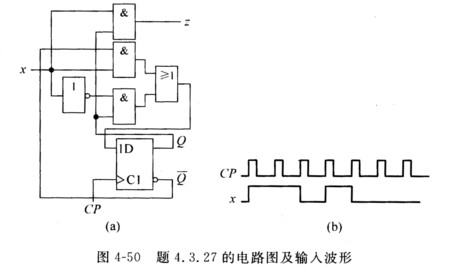

分析图4-50(a)所示同步时序电路。写出激励方程及输出方程,画出状态图,列出状态表。如初始状态为0,输入信号如图4-50(b)所示,画出D、Q、z的波形图。