更多“试用正边沿D触发器设计一时序电路,其状态图如图5.3.19所…”相关的问题

更多“试用正边沿D触发器设计一时序电路,其状态图如图5.3.19所…”相关的问题

第2题

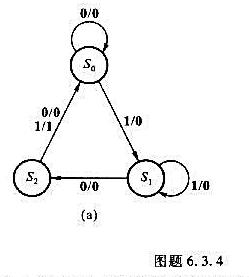

试用下降沿出发的D触发器设计一同步时序电路,状态图如6.3.4(a),S0,S1,S2的编码如6

试用下降沿出发的D触发器设计一同步时序电路,状态图如6.3.4(a),S0,S1,S2的编码如6

点击查看答案

.3.4(a)。

第3题

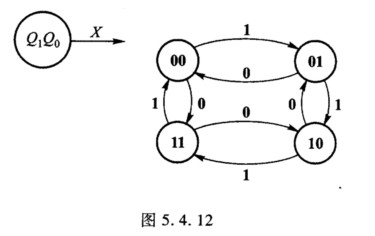

试用两个JK触发器按步骤设计一个同步时序电路。要求该电路有两个输入E、X。当E=0时,不管X的值等于几,触发器状

态都保持不变;当E=1时,若X=0,则触发器状态按00,01,10,11顺序循环;若X=1,则触发器状态按11,10,01,00顺序循环。

点击查看答案

第4题

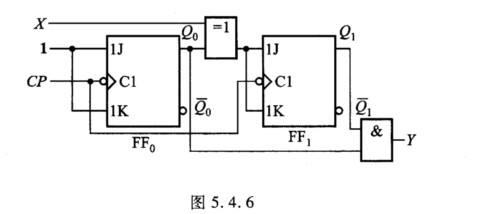

试用同步时序电路分析方法分析图5.4.6所示电路,画出状态图和波形图,确定电路的逻辑功能(设触发器

试用同步时序电路分析方法分析图5.4.6所示电路,画出状态图和波形图,确定电路的逻辑功能(设触发器的初始状态均为0)。

第7题

实现同一功能的Mealy型同步时序电路比Moore型同步时序电路所需要的()。

实现同一功能的Mealy型同步时序电路比Moore型同步时序电路所需要的()。

点击查看答案

A、状态数目更多

B、状态数目更少

C、触发器更多

D、触发器一定更少

第8题

用触发器实现同步时序电路。 (1)用J-K触发器设计一个模为8的格雷码同步计数器。 (2)用D

用触发器实现同步时序电路。 (1)用J-K触发器设计一个模为8的格雷码同步计数器。 (2)用D触发器设计上述题目。 (3)几点说明。

1.jpg)

如果结果不匹配,请

如果结果不匹配,请

1.jpg)