题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

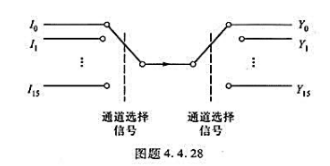

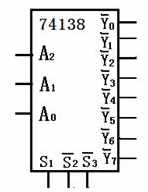

用3线-8线译码器74HC138和门电路设计1位二进制全减器电路。输入为被减数、减数和来自低位的借位;输出为两数之

用3线-8线译码器74HC138和门电路设计1位二进制全减器电路。输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号。

答案

答案

1位二进制全减器的输入信号有3个被减数A,减数B及来自低位的借位C0,输出信号有本位的差值S和向高位的借位C。

由题意可列出全减器的输出与输入之间的真值表,如表4.14所示。

| 表4.14 | |||||||||

| A1 | B1 | C0 | S1 | C1 | A1 | B1 | C0 | S1 | C1 |

| 0 0 0 0 | 0 0 1 1 | 0 1 0 1 | 0 1 1 0 | 0 1 1 1 | 1 1 1 1 | 0 0 1 1 | 0 1 0 1 | 1 0 0 1 | 0 0 0 1 |

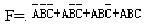

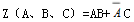

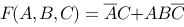

S1=A'1B'1 C0+A'1B1C'0+A1B1C'0+A1B1C0=m1+m2+m4+m7

C1=A'1B'1C0+A'1B1C'0+A'1B1C0+A1B1 C0=m1+m2+m3+m7由此可用74HC138实现该全减器电路,如图4.14所示。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“用3线-8线译码器74HC138和门电路设计1位二进制全减器…”相关的问题

更多“用3线-8线译码器74HC138和门电路设计1位二进制全减器…”相关的问题

的功能时,74138的输出端()连接与非门。

的功能时,74138的输出端()连接与非门。

的电平信号应是().

的电平信号应是().1.jpg)