更多“用GAu6V8器件实现一个3线一8线译码器。”相关的问题

更多“用GAu6V8器件实现一个3线一8线译码器。”相关的问题

第1题

用4片8线一3线优先编码器74LS148接成一个32线一5线优先编码器。可以附加必要的门电路。74LS148的逻辑框图见4.2.2节中的图4.2.8,它的功能表见表4.2.5。

用4片8线一3线优先编码器74LS148接成一个32线一5线优先编码器。可以附加必要的门电路。74LS148的逻辑框图见4.2.2节中的图4.2.8,它的功能表见表4.2.5。

点击查看答案

第4题

用VHDL描述下列器件的功能: (1)4选1数据选择器; (2)2线-4线译码器; (3)时钟R-S触

用VHDL描述下列器件的功能: (1)4选1数据选择器; (2)2线-4线译码器; (3)时钟R-S触发器; (4)带复位端Clear和置位端Preset、延迟Tpd为20ns的响应CP下降沿的J-K触发器; (5)主从J-K触发器; (6)集成计数器74163; (7)集成移位寄存器74194。

第5题

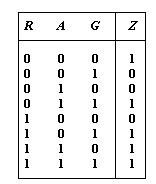

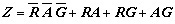

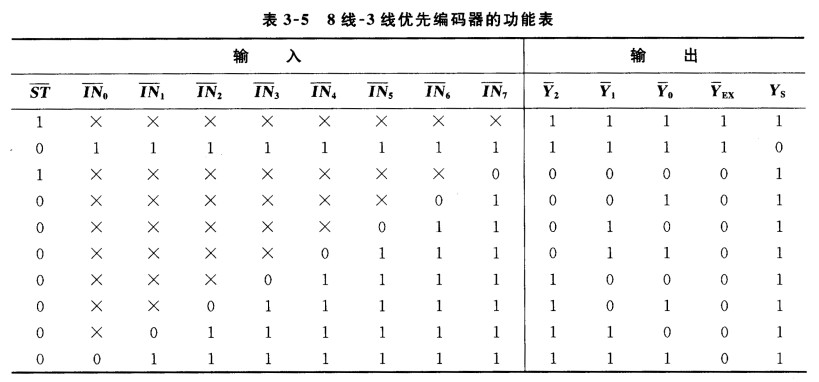

设计一个监控交通信号灯工作状态的逻辑电路。每一组信号灯由红、黄、绿三盏灯R,A,G组成。正常工作时,任何时候只有一盏灯亮,而其它状态时,电路发生故障,要求发出故障信号Z,以提示维护人员前去修理。下面给出的设计过程存在错误的是()。

A、真值表:

B、真值表:

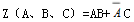

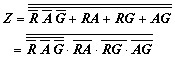

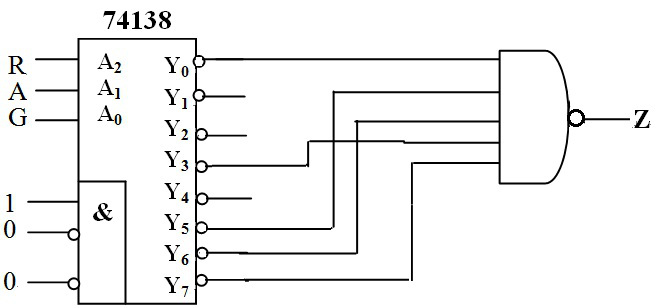

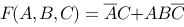

C、逻辑函数表达式:

D、利用与非门设计实现:

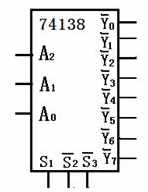

E、利用3线-8线译码器芯片74138及基本逻辑门设计实现:

第8题

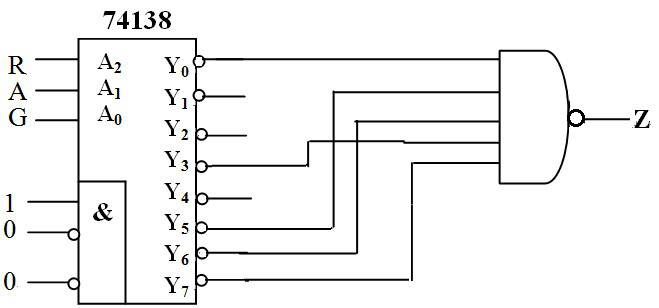

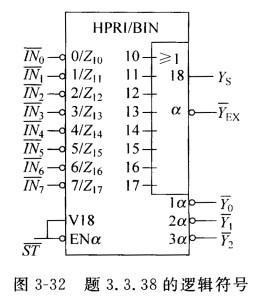

图3—32所示是8线-3线优先编码器74148的逻辑符号,其功能表如表3-5所示。试用以构成一个16线-4线优

图3—32所示是8线-3线优先编码器74148的逻辑符号,其功能表如表3-5所示。试用以构成一个16线-4线优先编码器。

第9题

试用输出低电平有效的3线-8线译码器和逻辑门设计一组合电路。该电路输入X,输出F均为3位二进制数。二者之间关

试用输出低电平有效的3线-8线译码器和逻辑门设计一组合电路。该电路输入X,输出F均为3位二进制数。二者之间关系如下:

2≤X≤5时,F=X+2

X<2时,F=1

X>5时,F=0

第10题

用3线-8线译码器74HC138和门电路设计1位二进制全减器电路。输入为被减数、减数和来自低位的借位;输出为两数之

用3线-8线译码器74HC138和门电路设计1位二进制全减器电路。输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号。

如果结果不匹配,请

如果结果不匹配,请

的功能时,74138的输出端()连接与非门。

的功能时,74138的输出端()连接与非门。