题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

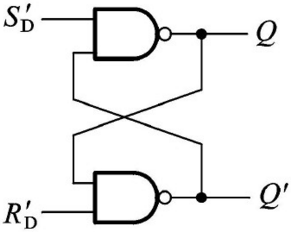

画出图5.1.1由与非门组成的SR锁存器输出端Q、Q'的电压波形,输入端S'D、R'D的电压波形如图5.1.1所

画出图5.1.1由与非门组成的SR锁存器输出端Q、Q'的电压波形,输入端S'D、R'D的电压波形如图5.1.1所示。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

画出图5.1.1由与非门组成的SR锁存器输出端Q、Q'的电压波形,输入端S'D、R'D的电压波形如图5.1.1所示。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“画出图5.1.1由与非门组成的SR锁存器输出端Q、Q'…”相关的问题

更多“画出图5.1.1由与非门组成的SR锁存器输出端Q、Q'…”相关的问题

欲使与非门构成的基本SR锁存器保持原态不变,则输入信号应为()。

A.S=R=0

B.S=R=1

C.S=1,R=0

D.S=0,R=I

在图所示的由与非门组成的基本RS触发器中,加入图示的S和R波形,画出触发器Q和

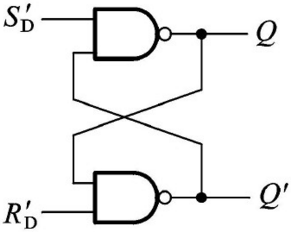

图4-28(a)、(b)为两种锁存器的原理图,设输入信号如图4-28(c)所示,且各门电路均有延迟tpd,试画出这两种电路的有关各点a、b、c以及输出端M的波形,说明图4-28(b)所示电路的缺点。设M的初态为0。

在下列锁存器和触发器中,没有约束条件的是()。

A.基本SR锁存器

B.主从SR触发器

C.逻辑门控SR触发器

D.边沿D触发器

对于用两个或非门构成的基本SR锁存器,如果S=R=0,则触发器的状态应为()。

A.置0

B.置1

C.不变

D.不定

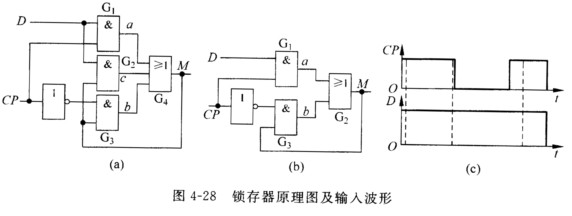

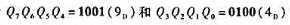

试用1片八D锁存器74HC373设计一个能锁存两组BCD码信号的锁存电路。假定三态输出使能端 ,锁存器原输出为

,锁存器原输出为 ,输入为

,输入为 ,画出锁存器锁存新数据前、后使能端LE应输入的波形和相应Q0的波形。

,画出锁存器锁存新数据前、后使能端LE应输入的波形和相应Q0的波形。

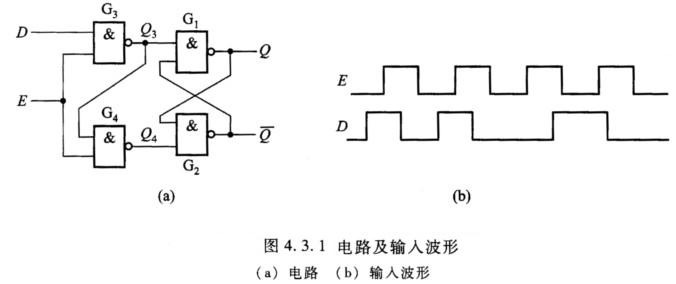

逻辑门控D锁存器及其输入端D、E的电压波形分别如图4.3.1(a)、(b)所示,分析该电路的逻辑功能,并对应输入电压波形画出输出端Q和

的电压波形,设电路的初始状态为0。

的电压波形,设电路的初始状态为0。